**Band 402**

Verlagsschriftenreihe des Heinz Nixdorf Instituts Prof. Dr.-Ing. Christoph Scheytt (Hrsg.) Schaltungstechnik

**Liang Wu**

# Ultrabroadband Sampling Circuits in SiGe BiCMOS Technology for Time Interleaved Analog-to-Digital Converters

Ultrabroadband Sampling Circuits in SiGe BiCMOS Technology for Time Interleaved Analog-to-Digital Converter

Ultrabreitbandige Sampler in SiGe-BiCMOS-Technologie für Analog-Digital-Wandler mit zeitversetzter Abtastung

#### Bibliografische Information Der Deutschen Bibliothek

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie; detaillierte bibliografische Daten sind im Internet über http://dnb.ddb.de abrufbar.

Band 402 der Verlagsschriftenreihe des Heinz Nixdorf Instituts

© Heinz Nixdorf Institut, Universität Paderborn – Paderborn – 2021

ISSN (Online): 2365-4422 ISBN: 978-3-947647-21-7

Das Werk einschließlich seiner Teile ist urheberrechtlich geschützt. Jede Verwertung außerhalb der engen Grenzen des Urheberrechtsgesetzes ist ohne Zustimmung der Herausgeber und des Verfassers unzulässig und strafbar. Das gilt insbesondere für Vervielfältigung, Übersetzungen, Mikroverfilmungen, sowie die Einspeicherung und Verarbeitung in elektronischen Systemen.

Als elektronische Version frei verfügbar über die Digitalen Sammlungen der Universitätsbibliothek Paderborn.

Satz und Gestaltung: Liang Wu

# Ultrabroadband Sampling Circuits in SiGe BiCMOS Technology for Time Interleaved Analog-to-Digital Converter

zur Erlangung des akademischen Grades eines

DOKTORS DER INGENIEURWISSENSCHAFTEN (DR.-ING.)

der Fakultät Elektrotechnik, Informatik und Mathematik

der Universität Paderborn

genehmigte

DISSERTATION

von

M.Sc. Liang Wu

Paderborn

Tag des Kolloquiums: 05.10.2021

Referent: Prof. Dr.-Ing. J. Christoph Scheytt Korreferent: Prof. Dr.-Ing. Manfred Berroth

#### **Abstract**

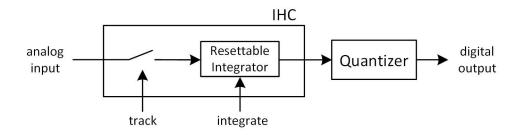

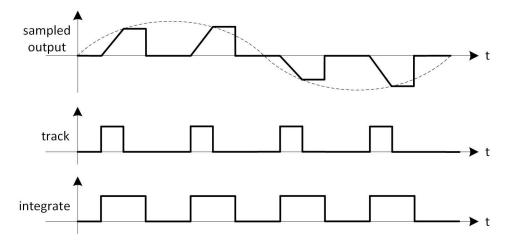

This work investigates ultra-broadband sampling techniques for time-interleaved analog-to-digital converters. The sampling techniques are mathematically analyzed in detail and compared with each other. The mathematical analysis allows to predict multiple sampler characteristics including sampler bandwidth, sampling precision and so on. Two different sampling techniques are studied. The conventional sampling technique is implemented with a track and hold amplifier (THA) using switched emitter follower sampling topology. As an alternative sampling technique the short-time-integration (STI) technique using an integrate-and-hold circuit (IHC) is implemented. Three samples chips (2 THA chips and 1 IHC chip) were fabricated in state-of-the-art 130 nm SiGe BiCMOS technology. The measured results exceed the state of the art in samplers wrt. bandwidth and effective resolution (effective number of bits, ENOB).

#### Zusammenfassung

Diese Arbeit untersucht Ultrabreitband-Abtasttechniken für zeitversetzte Analog-Digital-Wandler. Die Abtasttechniken werden mathematisch detailliert analysiert und miteinander verglichen. Die mathematische Analyse ermöglicht die Vorhersage mehrerer Sampler-Eigenschaften, einschließlich Sampler-Bandbreite, Sampling-Präzision usw. Zwei verschiedene Abtasttechniken werden untersucht. Die konventionelle Abtasttechnik wird mit einem Track-and-Hold-Verstärker (THA) unter Verwendung einer geschalteten Emitterfolger (SEF) Abtasttopologie implementiert. Als alternative Abtasttechnik wird die short-time-integration (STI) Abtasttechnik, die eine Integrier-und-Halteschaltung (integrate-and-hold circuit, IHC) benutzt, implementiert. Drei Sampler-Chips (2 THA-Chips und 1 IHC-Chip) werden in einer modernen 130 nm SiGe BiCMOS Technologie hergestellt. Die Messergebnisse übertreffen den Stand des Technik im Hinblick auf Bandbreite und effektive Auflösung (effective number of bits, ENOB).

Contents

## Ultrabroadband Sampling Circuits in SiGe BiCMOS Technology for Time Interleaved Analog-to-Digital Converters

### **Contents**

| 1 | Intro | oductio |                                                           |

|---|-------|---------|-----------------------------------------------------------|

|   | 1.1   | Motiva  |                                                           |

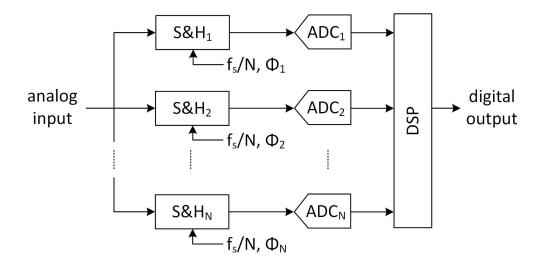

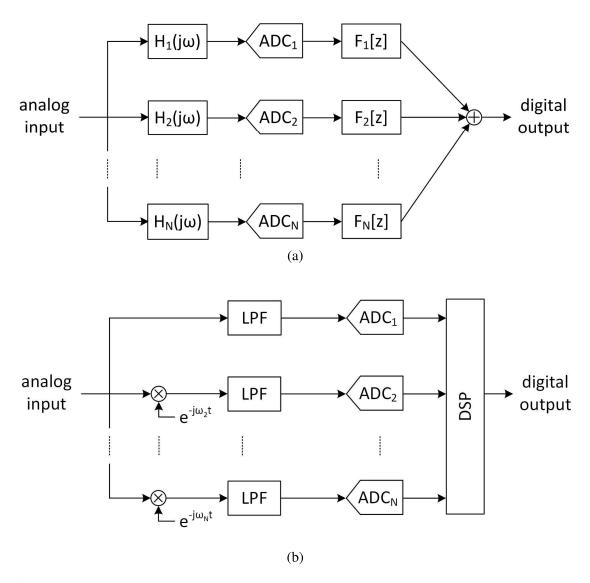

|   |       | 1.1.1   | TI ADC vs. FI ADC                                         |

|   |       | 1.1.2   | Challenges in TI ADC Design                               |

|   | 1.2   | Outline | e of the Thesis                                           |

| 2 | Sam   | pling ( | Circuit Fundamentals 5                                    |

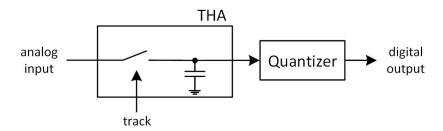

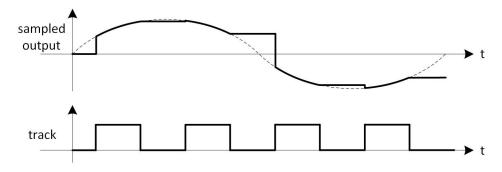

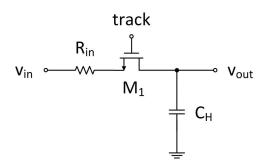

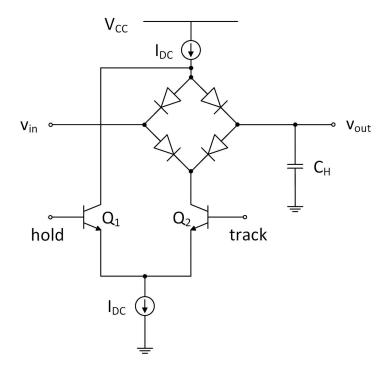

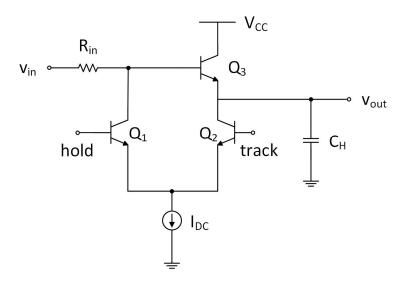

|   | 2.1   | TH Sa   | mpling Technology                                         |

|   |       | 2.1.1   | Principle of TH Sampling                                  |

|   |       | 2.1.2   | TH Sampling Topology                                      |

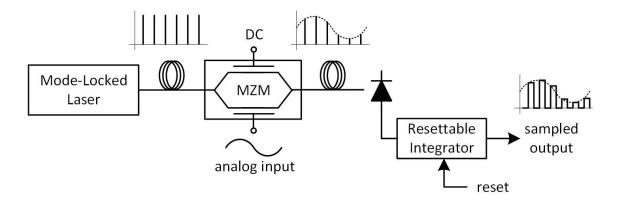

|   | 2.2   | Charg   | e Sampling Technology                                     |

|   |       | 2.2.1   | Principle of Charge Sampling                              |

|   |       | 2.2.2   | Charge Sampling Topology                                  |

|   | 2.3   | Comp    | arison of TH and Charge Sampler Characteristics           |

|   |       | 2.3.1   | Bandwidth                                                 |

|   |       | 2.3.2   | Sampling Jitter                                           |

|   |       | 2.3.3   | Noise                                                     |

|   |       | 2.3.4   | Droop                                                     |

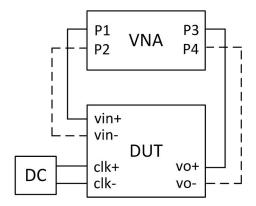

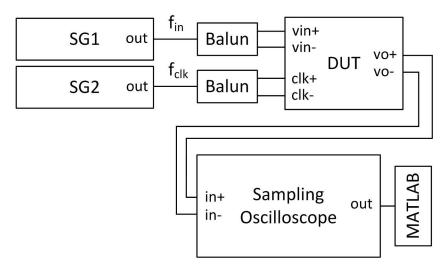

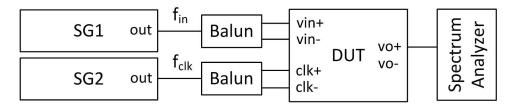

|   | 2.4   | Measu   | rement Techniques for Samplers                            |

|   |       | 2.4.1   | Small-Signal Measurement                                  |

|   |       | 2.4.2   | Large-Signal Measurement                                  |

|   | 2.5   | State   | of the Art in Ultra-broadband Sampling Circuits           |

|   | 2.6   |         | usion                                                     |

|   |       |         |                                                           |

| 3 | Des   | ign, Re | ealization, and Measurement of an SEF-based Input-Buffer- |

|   |       | s THA   | 25                                                        |

|   | 3.1   | Prelim  | inary considerations                                      |

|   |       | 3.1.1   | Microstrip Transmission Lines                             |

|   |       | 3.1.2   | Inductive Peaking                                         |

|   |       | 3.1.3   | Emitter Follower                                          |

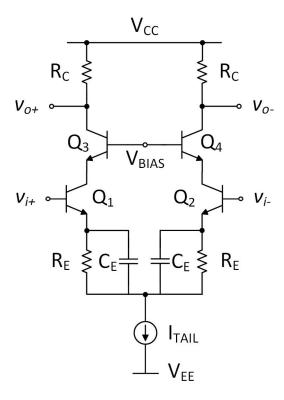

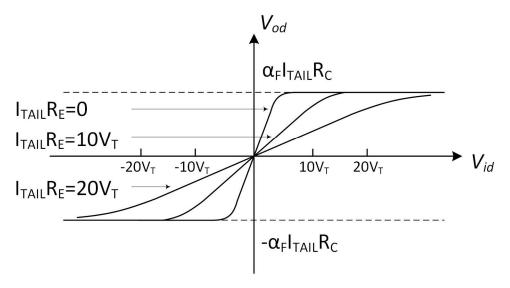

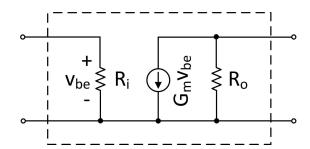

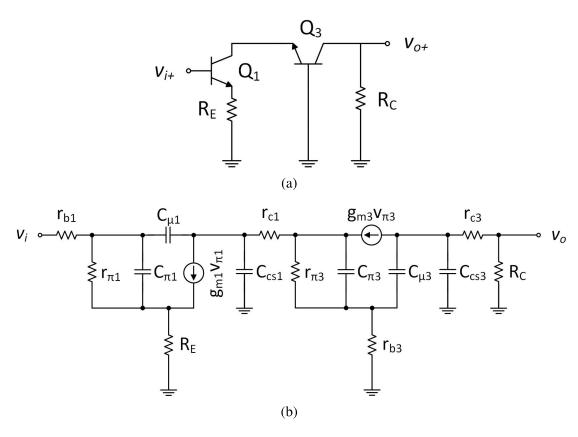

|   |       | 3.1.4   | Differential Amplifier                                    |

|   | 3.2   | Schen   | natic Analysis and Design                                 |

|   |       | 3.2.1   | SEF as Input Stage                                        |

|   |       | 3.2.2   | Output Buffer                                             |

II Contents

|   |                            | 3.2.3                                                                                                             | Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34                                                                |

|---|----------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| ; | 3.3                        | Layout                                                                                                            | and Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35                                                                |

| ; | 3.4                        | Measu                                                                                                             | rement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36                                                                |

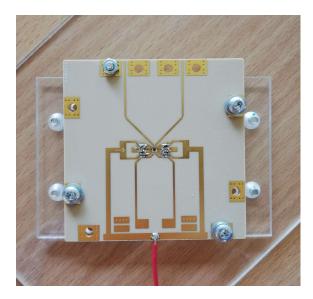

|   |                            | 3.4.1                                                                                                             | RF Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36                                                                |

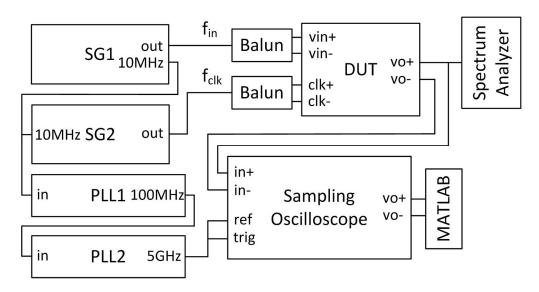

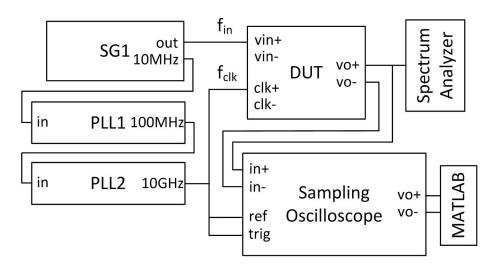

|   |                            | 3.4.2                                                                                                             | Test Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37                                                                |

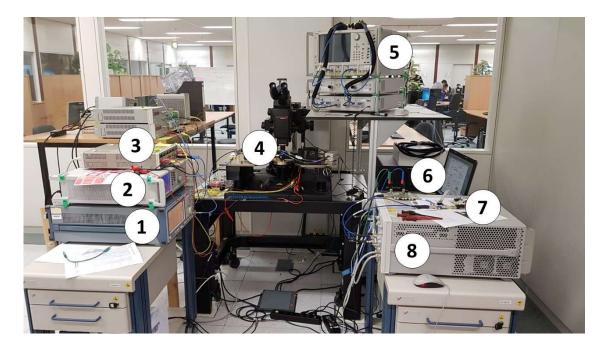

|   |                            | 3.4.3                                                                                                             | Test Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38                                                                |

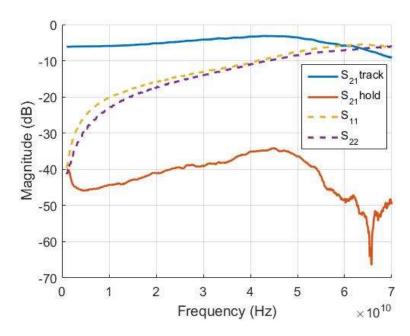

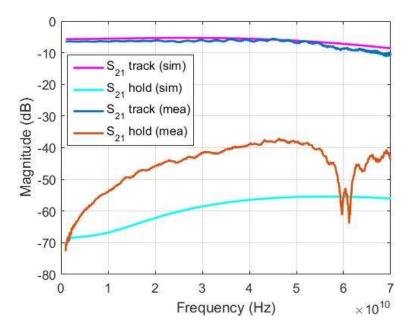

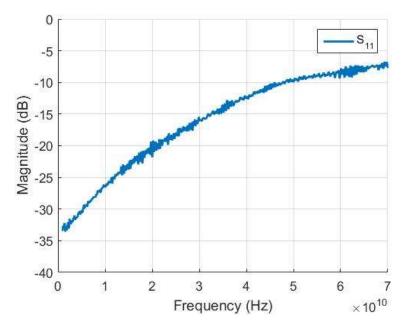

|   |                            | 3.4.4                                                                                                             | S-Parameter Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39                                                                |

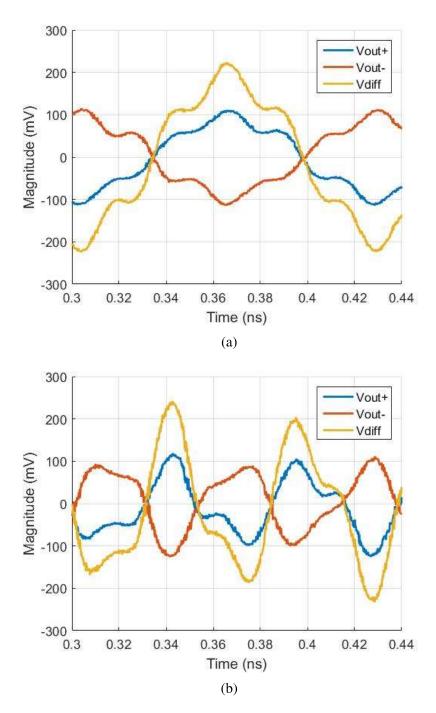

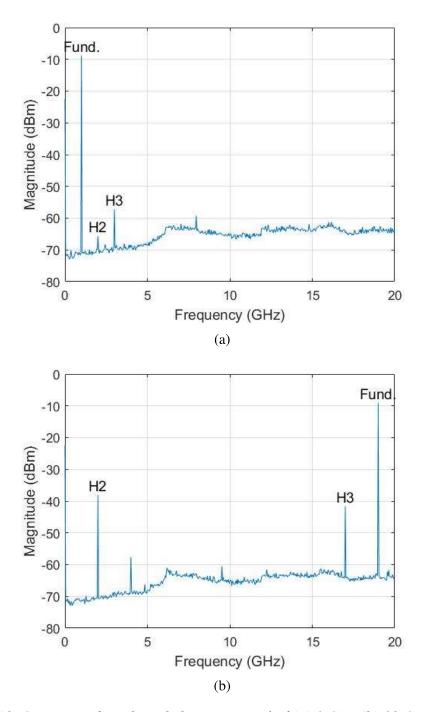

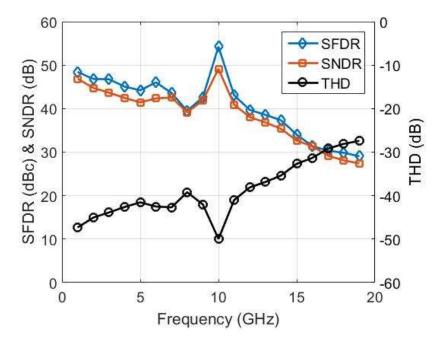

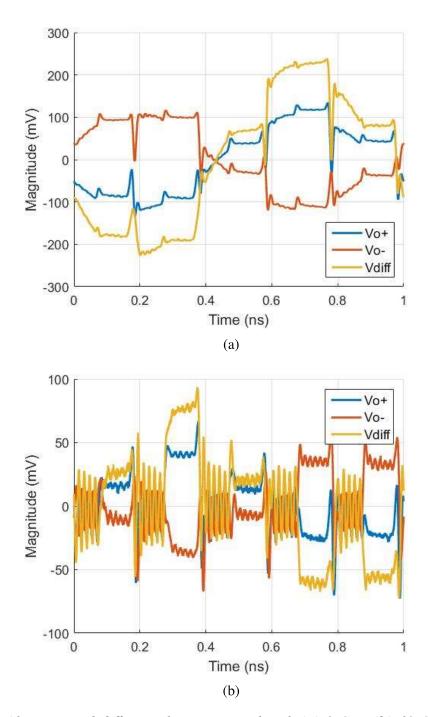

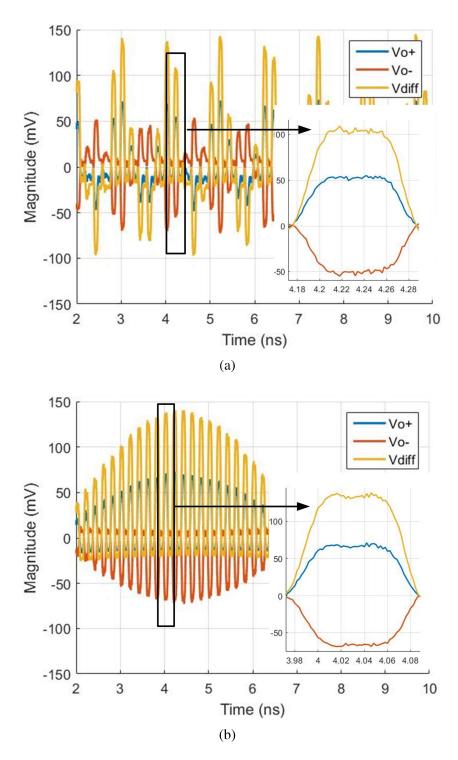

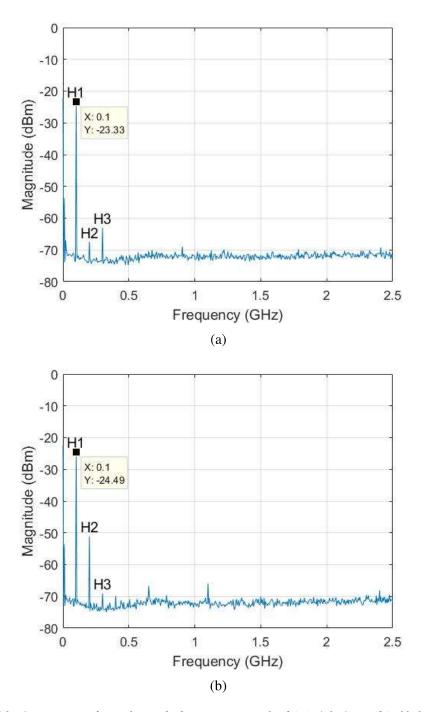

|   |                            | 3.4.5                                                                                                             | Transient and Spectrum Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40                                                                |

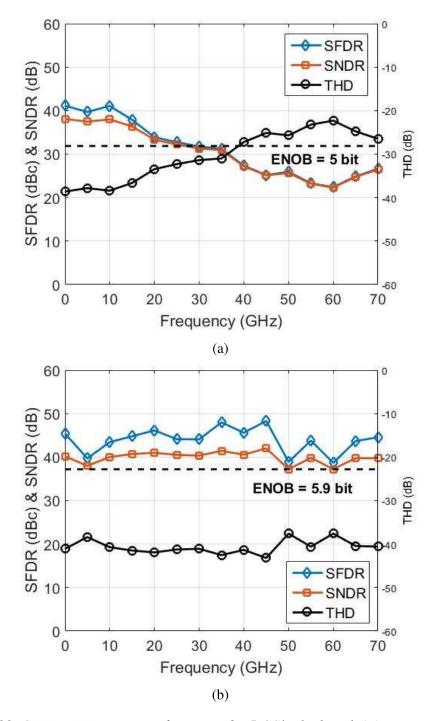

| ; | 3.5                        | Conclu                                                                                                            | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43                                                                |

|   |                            |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                   |

|   | Des<br>Buff                | •                                                                                                                 | alization, and Measurement of an SEF-based THA with Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45                                                                |

|   | 4.1                        |                                                                                                                   | inary considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                |

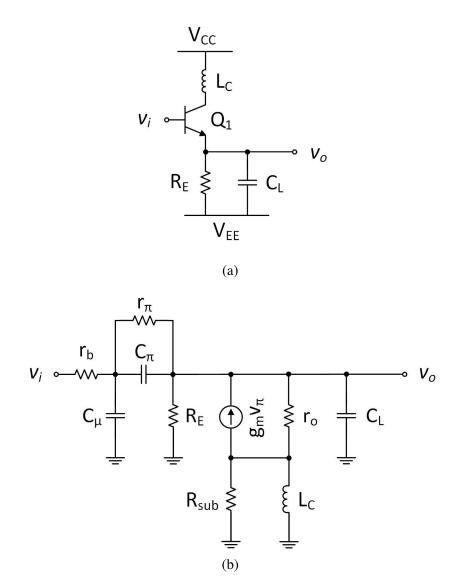

|   |                            | 4.1.1                                                                                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 45                                                                |

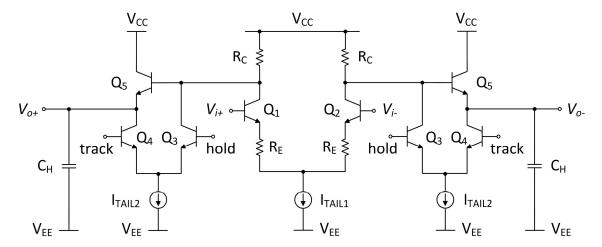

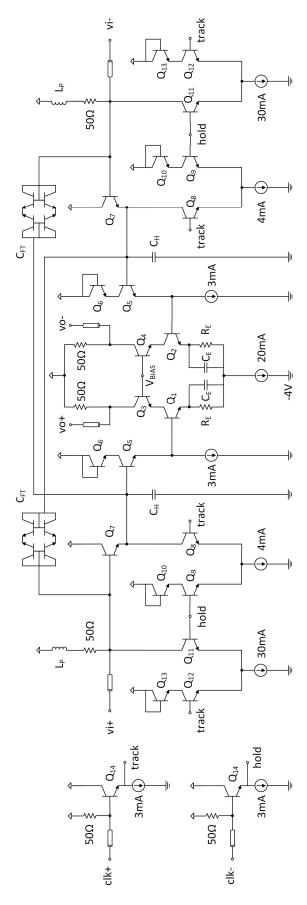

|   | 4.2                        | Schem                                                                                                             | natic Analysis and Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47                                                                |

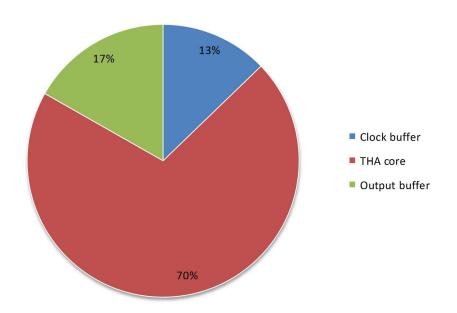

|   |                            |                                                                                                                   | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51                                                                |

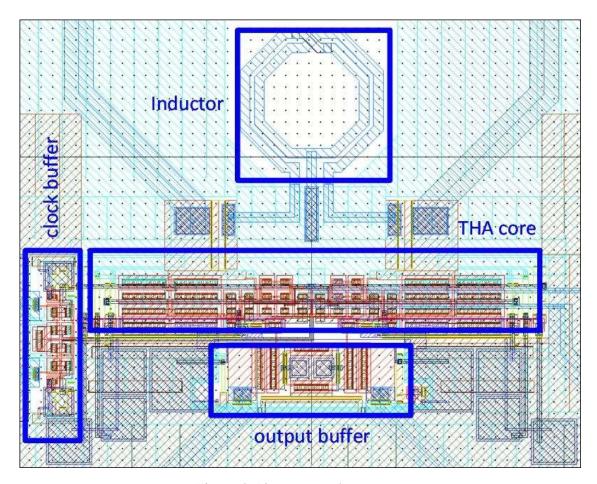

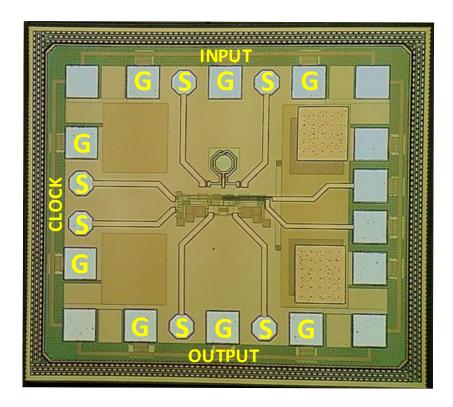

|   | 4.3                        |                                                                                                                   | and Chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 51                                                                |

|   | 4.4                        |                                                                                                                   | rement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                                |

|   |                            | 4.4.1                                                                                                             | RF Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53                                                                |

|   |                            | 4.4.2                                                                                                             | Test Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53                                                                |

|   |                            | 4.4.3                                                                                                             | S-Parameter Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55                                                                |

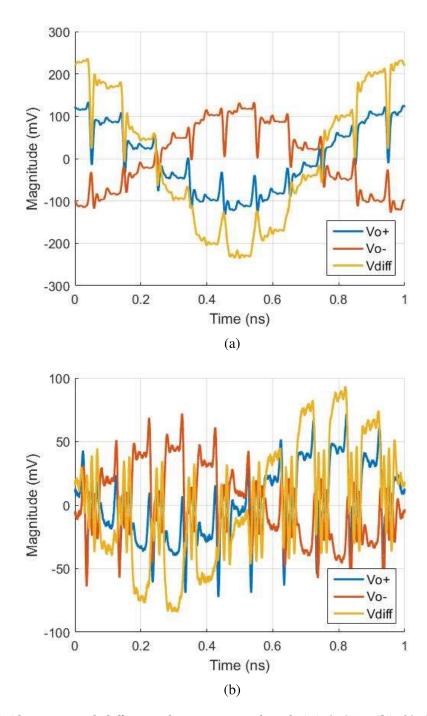

|   |                            |                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 55                                                                |

|   |                            | 4.4.4                                                                                                             | Transient and Spectrum Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | JJ                                                                |

|   | 4.5                        |                                                                                                                   | Transient and Spectrum Measurement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                                                                |

|   |                            | Conclu                                                                                                            | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 57                                                                |

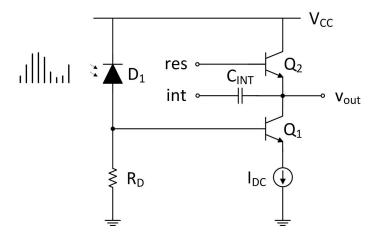

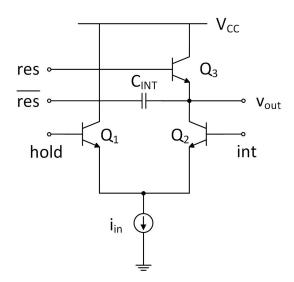

| 5 | Des                        | Concluign, Re                                                                                                     | alization, and Measurement of an STI Sampler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57<br><b>61</b>                                                   |

| 5 |                            | Conclu<br>ign, Re<br>Archite                                                                                      | alization, and Measurement of an STI Sampler ectures of STI Sampler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57 <b>61</b> 61                                                   |

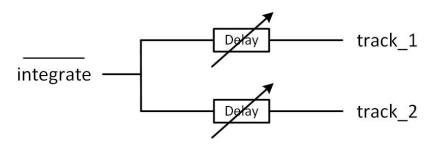

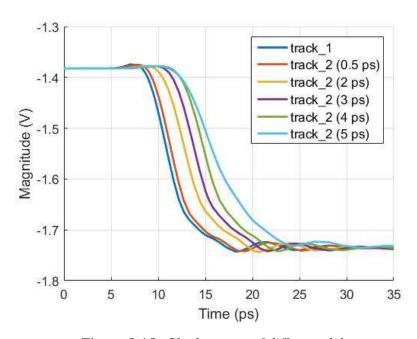

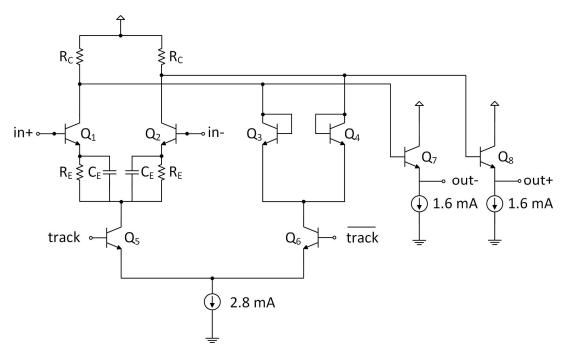

| 5 | Des                        | Concluign, Re<br>Archite<br>5.1.1                                                                                 | alization, and Measurement of an STI Sampler ectures of STI Sampler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57 <b>61</b> 61 61                                                |

| 5 | <b>Des</b><br>5.1          | Concluign, Re Archite 5.1.1 5.1.2                                                                                 | alization, and Measurement of an STI Sampler ectures of STI Sampler  Conventional Architectures of STI IHC with Single Delay Element Novel Architecture of STI IHC with Differential Delay Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57 <b>61</b> 61 61 61                                             |

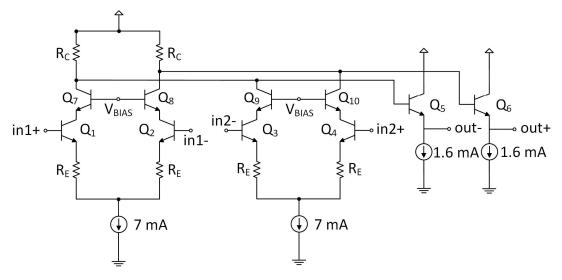

| 5 | Des                        | ign, Re Archite 5.1.1 5.1.2 Syster                                                                                | alization, and Measurement of an STI Sampler ectures of STI Sampler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 57 61 61 61 65                                                    |

| 5 | <b>Des</b><br>5.1          | ign, Re Archite 5.1.1 5.1.2 Syster 5.2.1                                                                          | alization, and Measurement of an STI Sampler ectures of STI Sampler Conventional Architectures of STI IHC with Single Delay Element Novel Architecture of STI IHC with Differential Delay Scheme .  In Analysis of STI Sampler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 57 61 61 61 65 65                                                 |

| 5 | <b>Des</b> i<br>5.1<br>5.2 | ign, Re Archite 5.1.1 5.1.2 Syster 5.2.1 5.2.2                                                                    | alization, and Measurement of an STI Sampler ectures of STI Sampler.  Conventional Architectures of STI IHC with Single Delay Element Novel Architecture of STI IHC with Differential Delay Scheme.  Analysis of STI Sampler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57 61 61 61 65 65 66                                              |